# **Capturing Video the Easy Way**

Programming FPGAs for flexible, quick applications development

| Summary                                  | This tutorial is based on the TRAININGcenter Video of the same title and provides a step by step overview of how to create a reasonably sophisticated FPGA design. It                    |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorial<br>TU0131 (v2.0) March 20, 2008 | outlines how to create a design using OpenBus, Constraining the Design to a target device, developing embedded software using DSF, and running the entire design on a Desktop NanoBoard. |

FPGAs have been around for over 20 years but for many designers they are still a 'new thing'. Coming to grips with the technology and their capabilities can sometimes feel like a daunting task but regardless of your current skill levels, this tutorial will walk you through the process of creating a reasonably sophisticated FPGA design from start to finish. In doing so, you'll be provided with an overview of several of the features of Altium Designer that have been specifically developed to increase productivity and to make the design process easier. These include:

- OpenBus system development

- Autoconfiguration of FPGA projects

- Device Software Framework

You'll also be shown how to interact with some of the advanced Desktop NanoBoard peripherals such as:

- Composite video capture

- Touchscreen TFT display

#### What you'll be creating

This tutorial is based around a video capture and display application.

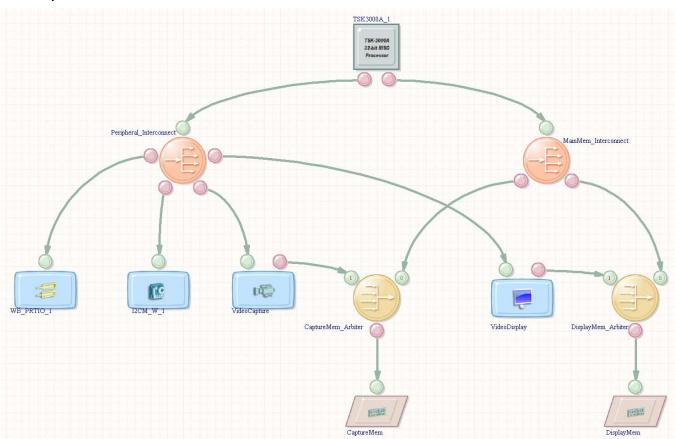

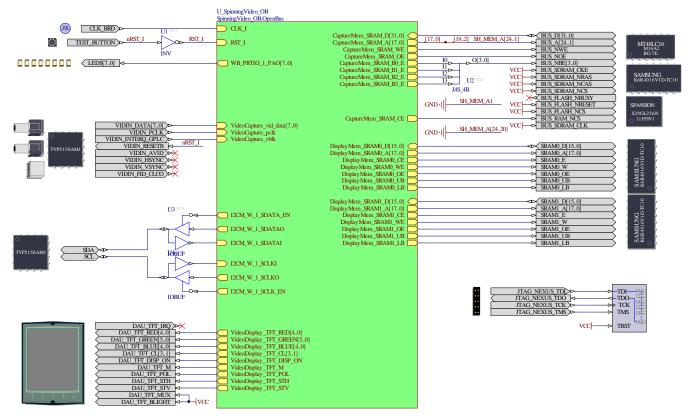

Figure 1. Overview of the Video capture system

### What you'll need

In order to complete this tutorial, you'll need:

- Altium Designer 6.8 (or later) installed

- A Desktop NanoBoard with PB01 peripheral board and DB30 Spartan3 daughter board (or similar) installed.

- A composite video source from a camera or DVD player.

- Vendor build tools. The free version of Xilinx's ISE (8.2.03i or later) will be sufficient if you are using the DB30 daughter board.

## **Creating the FPGA Project**

To start working with Altium Designer, you first need a project. A project makes managing your source design documents and any generated outputs much easier. For FPGA designs, you'll need an FPGA project.

To create a new FPGA project:

- 1. Select File » New » Project » FPGA Project from the menus, or click on Blank Project (FPGA) in the New section of the Files panel.

- The Projects panel will display a new FPGA project with the default name FPGA\_Project1.PrjFpg. Select File » Save Project or right-click the project in the Projects panel and select the Save Project item. Save the file as SpinningVideo.PrjFpg.

To avoid problems that some of the FPGA build tools have with spaces (' ') in filenames, use underscores ('\_') instead of spaces.

### Adding source documents to the FPGA Project

An FPGA project supports three types of source documents – Schematic, HDL (Verilog or VHDL) and OpenBus. You can use a mixture of all three document types in a project with the use of sheet symbols. However, for FPGA projects, you *must* have a schematic as the top level document. This is necessary for supporting FPGA-to-PCB integration and synchronization.

To create a single schematic document and add it to the project:

- 1. Select File » New » Schematic, or click on Schematic Sheet in the New section of the Files panel. A blank schematic sheet named Sheet1.SchDoc displays in the design window

- 2. Rename the new schematic file (with a .SchDoc extension) by selecting File » Save As. Navigate to the same folder as your project and type the name SpinningVideo\_FPGA.SchDoc and click on Save.

We'll come back to this document shortly but for now, we need to also create a new OpenBus document and add that to the project as well.

To create a single OpenBus document and add it to the project:

- Select File » New » Other » OpenBus System Document, or click on OpenBus System Document in the New section of the Files panel. A blank OpenBus document named System1.OpenBus displays in the design window

- Rename the new OpenBus document (with an .OpenBus extension) by selecting File » Save As. Navigate to the same folder as your project and type the name SpinningVideo\_OB.OpenBus and click on Save.

## Defining an FPGA system using OpenBus

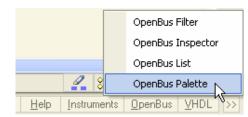

OpenBus is a new way of doing system-level FPGA design. It offers a much lighter interface than schematic based implementations but without becoming lightweight in its capabilities. By automatically taking care of much of the low-level detail, it lets you focus on the high-level system and interconnection of major components. You'll find all of the components you need in the **OpenBus Palette** panel. You can display the panel by clicking on the OpenBus panel control in the lower right portion of the main editor and then selecting the **OpenBus Palette** item from the popup menu.

### **Placing OpenBus Components**

The **OpenBus Palette** panel contains all OpenBus components that can be used in an OpenBus document. They have been categorized in the palette into groups of Connectors, Processors, Memories and Peripherals. The subsections can be expanded or collapsed using the S or S icons respectively.

For this tutorial, we'll be using the following components:

|   | 🔻 🦉 🗙     |

|---|-----------|

| - | Workspace |

|   | Project   |

|   | • ال      |

|   |           |

|   |           |

|   |           |

|   |           |

|   | T         |

Figure 2. Projects Panel with FPGA project and newly created documents

Figure 3. Accessing the OpenBus Panels

Warning: Do not use spaces or dashes ('-') in file or project names. Use underscores if necessary.

| OpenBus Palette V X                                                                                                                                                                    | Group       | Item                      | lcon                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------|--------------------------------------------------------------------|

| Atbiter Bus Exporter Bus Importer                                                                                                                                                      | Connectors  | Arbiter                   |                                                                    |

| Dual Port Interconnect Port Terminator                                                                                                                                                 | Connectors  | Interconnect              | -E                                                                 |

| RM720T_LH795: COREMP7 MICROBLAZE<br>ANTERA.<br>Nios'II Nios'II<br>NIOS2e NIOS2f NIOS2s                                                                                                 | Processors  | TSK3000A                  | TSK-3000A<br>32-bit RISC<br>Processor                              |

| XILINK     Image: Arrowski state       PowerRC     Processor       PPC405A     PPC405CR       TSK3000A                                                                                 | Memories    | SRAM Controller           |                                                                    |

| BRAM Controller<br>Controller SRAM<br>Controller<br>Shared Memory SRAM Controller<br>Controller                                                                                        | Peripherals | Port IO                   | 00                                                                 |

| Repripherals         ASP       Image: Controller Controller         ASP       Audio Streaming CAN Controller         CONN       Image: Controller         CONN       Image: Controller | Peripherals | Video Capture Controller  | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |

| CAN Controller Dual Timer Unit EMAC(32)<br>(B) EMAC(32)<br>EMAC(8) 10-100 EMAC(8) 10-100 I2CM Controller<br>MD                                                                         | Peripherals | VGA 32-Bit TFT Controller |                                                                    |

| IDE Controller<br>IEEE754<br>Roating Point<br>Projects<br>OpenBus Palette<br>Files                                                                                                     | Peripherals | I2CM Controller           | IG                                                                 |

Figure 4. OpenBus components required for this tutorial

To place an OpenBus component onto an OpenBus Document:

- 1. Select the OpenBus Component that you want to place by left-clicking on its icon once in the **OpenBus Palette** panel.

- 2. The component will be locked to the mouse cursor. At this point you can use the **Spacebar** to rotate the component or the **X** or **Y** keys to flip the component along the X or Y axis respectively.

- 3. Move the mouse to where you want the component placed and left-click the mouse once again to place it. The cursor will remain in placement mode so that you can continue to place several more instances of the same components if required.

- 4. Press the **Esc** key or right-click the mouse to exit the placement mode.

- 5. Continue placing the components indicated in Figure 4 as per the OpenBus diagram of Figure 5.

- To edit the names of the OpenBus components that you have placed:

- 1. Click once on the text associated with the OpenBus component that you want to rename. This selects the text.

- 2. Click a second time on the text or press the F2 key to enter the edit text mode.

- 3. Edit the text as desired.

- 4. Press the Enter key or click on something else in the editor window to leave the editing mode and keep your changes.

### **Connecting OpenBus Components**

In order to control the flow of data between the components on your OpenBus document, you will need to place connection links

between them. These links indicate bus connections between master ports and slave ports. The arrow on the connection link indicates the direction of control.

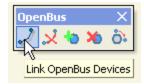

To place a connection link between a master and slave port:

- 1. Select **Tools** » **Link OpenBus Ports** or click on the Link OpenBus Devices icon in the **OpenBus** toolbar.

- 2. Click the master port that you want to create the link from

- 3. Click on the slave port that you want to be controlled.

- 4. Repeat steps 2 & 3 for any additional links that you wish to create. To exit link placement mode, hit the **Esc** key or right-click the mouse.

To remove a connection link between a master and slave port:

- 1. Select **Tools** » **Remove OpenBus Link** or click on the Remove OpenBus Link icon in the **OpenBus** toolbar.

- 2. Hover the mouse over the link that you wish to remove until it changes color. Click the leftmouse button to execute the link removal.

- 3. Repeat step 2 for any additional links that you wish to remove. To exit the link removal mode, hit the **Esc** key or right-click the mouse.

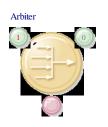

### **Interconnect and Arbiter Components**

Because connection links can only be made between a single master and a single slave, OpenBus Interconnect and Arbiter components are required to allow you to connect multiple components together.

OpenBus Interconnect components have a single slave port and one or more master ports. This allows a master device (connected to the OpenBus Interconnect's slave port) to control multiple other slave devices (connected to the OpenBus Interconnect's master ports).

OpenBus Arbiters are the complement to Interconnect Components. They allow multiple master components to control a single device such as when you need to connect multiple master components to a single block of memory. The Arbiter component is responsible for coordinating accesses between the competing masters. You can control how it performs its arbitration by right-clicking the component and ration options.

accessing its configuration options.

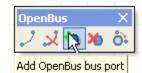

To add an additional port to an OpenBus Interconnect or Arbiter component:

- 1. Select **Tools** » **Add OpenBus Port** or click on the Add OpenBus Port icon in the **OpenBus** toolbar.

- 2. Hover the mouse over an existing port on the component you wish to add a new port to. A red line will appear indicating where the port will be added.

- 3. Click to add the new port.

- 4. Repeat steps 2 & 3 for any additional ports that you wish to create. To exit the port placement mode hit the **Esc** key or rightclick the mouse.

To remove a port from an OpenBus Interconnect or Arbiter component:

- 1. Select **Tools** » **Remove OpenBus Port** or click on the Remove OpenBus bus port icon in the **OpenBus** toolbar.

- 2. Hover the mouse over the port that you wish to remove until a red cross appears. Click the leftmouse button to execute the port removal.

- 3. Repeat step 2 for any additional ports that you wish to remove. To exit the port removal mode, hit the **Esc** key or right-click the mouse.

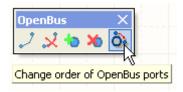

OpenBus

Remove OpenBus Link

To change the position of ports on an OpenBus Interconnect or Arbiter component:

- 1. Select **Tools** » **Reorder OpenBus Ports** or click on the Reorder OpenBus ports icon in the **OpenBus** toolbar.

- 2. Hover the mouse over the port that you wish to move until a red circle is drawn around it. Click the left-mouse button to begin the move.

- 3. Move the mouse cursor over another port on the component. A red line will appear at the location where the port will be moved to. Left click the mouse to execute the move.

- 4. Repeat steps 2 & 3 for any additional ports that you wish to move. To exit the port reorder mode, hit the **Esc** key or rightclick the mouse.

#### Completing the OpenBus System

1. Complete the creation of the OpenBus system using the techniques outlined above. The completed OpenBus system can be seen in Figure 5.

2. Save your work.

Figure 5. Completed OpenBus design for this tutorial

## **Configuring OpenBus Components**

The vast majority of components found in the OpenBus Palette translate directly to similarly named components found within the FPGA Peripherals and FPGA Processor libraries used for schematic-based FPGA design. In the same way that several of the components in the schematic-based libraries are configurable, so too are their OpenBus counterparts. In this tutorial, we are using several configurable components that will need to be adjusted.

### **Configure Peripheral Components**

To configure the Port I/O component for this tutorial:

- 1. Right-click the WB\_PRTIO\_1 component and select the Configure WB\_PORTIO\_1 (Port IO) ... item.

- 2. In the Configure OpenBus Port I/O dialog box:

- Set the port Kind to Output.

- Set the Port Count to 1.

- Set the Bus Width to 8.

- 3. Click **OK** to save the changes.

#### **Configure Memory Controllers**

To Configure the Video Capture Memory component:

- 1. Right-click the CaptureMem component and select the Configure CaptureMem (SRAM Controller) ... item.

- 2. In the Configure (Memory Controller) dialog box:

- Set the Memory Type to Asynchronous SRAM.

- Set the Size of Static RAM array to 1 MB (256K x 32-bit).

- Set the Memory Layout to 1 x 32-bit Wide Device.

- 3. Click **OK** to save your changes.

- To configure the Video Display Memory component:

- 1. Right-click the DisplayMem component and select the Configure DisplayMem (SRAM Controller) ... item.

- 2. In the Configure (Memory Controller) dialog box:

- Set the Memory Type to Asynchronous SRAM.

- Set the Size of Static RAM array to 1 MB (256K x 32-bit).

- Set the **Memory Layout** to **2 x 16-bit Wide Devices**.

- 3. Click OK to save your changes.

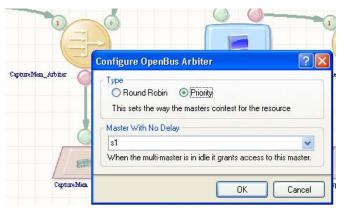

#### **Configure Memory Arbiters**

To configure the Capture Memory Arbiter component:

- 1. Right-click the CaptureMem\_Arbiter component and select the **Configure CaptureMem\_Arbiter (Arbiter) ...** item.

- 2. In the Configure OpenBus Arbiter dialog box:

- Set the Type to Priority.

- Set the Master With No Delay to be same slave port as the VideoCapture component is connected to (S1).

- 3. Click OK to save your changes.

- To configure the Display Memory Arbiter component:

- 1. Right-click the DisplayMem\_Arbiter component and select the **Configure DisplayMem\_Arbiter (Arbiter) ...** item.

- 2. In the Configure OpenBus Arbiter dialog box:

- Set the Type to Priority.

- Set the Master With No Delay to be same slave port as the VideoDisplay component is connected to (S1).

- 3. Click **OK** to save your changes.

Figure 7. Configuring an Arbiter component

Kind

Port Count

Bus Width

○ Input/Output

○ 1

○ 8

○ Tristate

○ 2

○ 16

○ Output

○ 4

○ 32

**?** ×

Figure 6. Configuring the IO Port peripheral

Configure OpenBus Port I/O

### **Configure the Processor**

To configure the TSK3000 processor component:

- 1. Right-click the TSK3000 component and select Configure TSK3000A\_1 (TSK3000) ...

- 2. In the Configure (32-bit Processors) dialog box:

- Confirm that the processor listed in the drop down box in the upper right is TSK3000.

- Set the Internal Processor Memory to 8 K Bytes (2K x 32-Bit Words).

- Set the Multiply/Divide Unit (MDU) to Hardware MDU.

- Set the On-Chip Debug System to Include JTAG-Based On-Chip Debug System and Disable Breakpoints on Hard Reset.

- 3. Click **OK** to save your settings and close the dialog box.

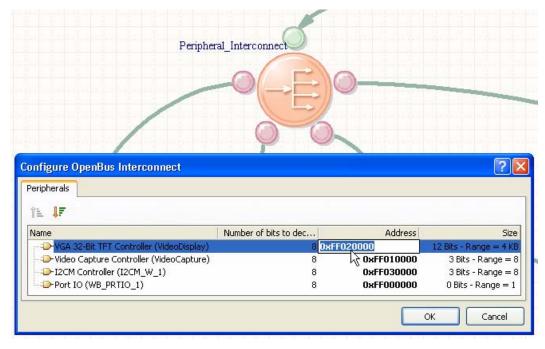

## Managing the Memory Map

One of the key benefits of developing your design with OpenBus is the level of automation that OpenBus brings to the management of the system memory map. Ultimately all peripherals and memory devices sit within a 32-bit memory space that spans 4GBytes. To make the management of this memory space easier, OpenBus intelligently interprets the design and automatically allocates memory spaces for each of the peripherals and memory controllers. In most situations these memory allocations will be sufficient but in some rare cases you may wish to manually edit the memory allocations yourself. You can still do this with OpenBus.

### **Configuring Memory using Interconnect Components**

Under normal circumstances, the interconnect component will probe the settings and memory requirements of each of its connected devices and will update the memory map automatically. You can see (and edit) the memory mapping of the interconnect component from the *Configure OpenBus Interconnect* dialog which can be accessed from the component's right-click menu.

Figure 8. Viewing (and editing) the interconnect memory map

The Interconnect configuration information is automatically propagated to the memory map of the processor.

### **Configuring Memory from within the Processor**

In addition to the memory that is managed by each of the interconnect components within the OpenBus document, you can also centrally manage memory from the Processor's memory and peripheral configuration dialog boxes. These can be accessed by right-clicking the processor.

The *Configure Processor Memory* dialog box provides a pictorial representation of where the peripherals and memory controllers will be positioned within the processor's memory. You can manually control the memory map using the grid control at the bottom of the dialog but this is usually unnecessary. A far simpler option is to check the **Automatically**

|                          | Configure TSK3000A_1 (TSK3000A) |

|--------------------------|---------------------------------|

| LA000ERS                 | ⊆onfigure Processor Memory      |

| 73K-300                  | Configure Processor Peripheral  |

| 32-bli Ribu<br>Processor |                                 |

| -00-                     |                                 |

Figure 9. Configuring the processor memory

**import when compiling** checkbox. This will ensure that all OpenBus memory settings are incorporated and synchronized in the design each time it is compiled.

Checking the **hardware.h** (C Header File) option will cause a hardware.h header file to be created when the project is compiled. This header file will be automatically added to any linked embedded projects and will provide macros that define where each of the peripherals and memory devices sit within memory. By ensuring these two checkboxes are checked, any changes you make to the OpenBus document will be propagated through to the embedded project as well.

| Archite                                                                                                                                    | ctural Layer                                         |             | Logical Layer                                        |                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------|------------------------------------------------------|-------------------------------------------|

| OxF                                                                                                                                        | FFF_FFFF                                             |             | OxFFFF_FFFF                                          |                                           |

|                                                                                                                                            | sor I/O Space<br>IO Port<br>e processor              | OxFFFF_FFFF | I2CM_W_1 (Peripheral)<br>Peripheral_Interconnect     | 0xFF03_0007<br>0xFF03_0000                |

| External-Memory Space Internal-Memory Where the boot code resides 0x0000_0000                                                              |                                                      | OXFEFO 000  | VideoDisplay (Peripheral)<br>Peripheral_Interconnect | 0xFF02_0FFF<br>0xFF02_0000                |

|                                                                                                                                            |                                                      |             | VideoCapture (Peripheral)<br>Peripheral_Interconnect | 0xFF01_0007<br>0xFF01_0000                |

|                                                                                                                                            |                                                      | 0x0100_0000 | WB_PRTI0_1 (Peripheral)<br>Peripheral_Interconnect   | 0xFF00_0000<br>0xFF00_0000                |

|                                                                                                                                            |                                                      | OX00FF_FFFF |                                                      | 0x9100_0000<br>0x0100_0000<br>0x00FF_FFFF |

|                                                                                                                                            |                                                      | 0x0000_0000 | 0x0000_0000                                          | 0x0000_0000                               |

| Name                                                                                                                                       | Address                                              | Δ           | Size Interrupts                                      |                                           |

| WB_PRTI0_1<br>/ideoCapture<br>/ideoDisplay<br>2CM_W_1                                                                                      | 0xFF000000<br>0xFF010000<br>0xFF020000<br>0xFF030000 | (<br>(      | 0x0001<br>0x0008<br>0x1000<br>0x0008                 |                                           |

| Generate following files into the subproject(s) at FPGA Project compilation<br>☐ hardware.asm (Assembly File) ☑ hardware.h (C Header File) |                                                      |             |                                                      |                                           |

Figure 10. Controlling how memory configuration information is propagated throughout the design.

To set the project to automatically import the settings from the OpenBus document:

- 1. Right-click the TSK3000 processor and select Configure Processor Memory ...

- 2. In the Configure Processor Memory dialog box, check the hardware.h checkbox.

- 3. Check the Automatically import when compiling checkbox also.

- 4. Click the **Configure Peripherals** button to change views. If asked if you want to save the configuration before moving to configuring the peripherals, click **Yes**.

- 5. Check the **Automatically import when compiling** checkbox to import the peripheral memory map when the project is compiled.

- 6. Click **OK** to exit.

## Linking the OpenBus Document to its Parent Schematic

As mentioned right back at the beginning of this tutorial, the top level document in an FPGA project needs to be a schematic. Now that we have created an OpenBus document, we must now link that document back to the top level schematic sheet that we created earlier on.

Before linking the documents, it's worth taking just a moment to explain how the underlying signals in the OpenBus document get exposed to the top level schematic. All of the signals used for the bus interconnects (links) will generally remain hidden within the OpenBus document but there are many other signals that are not immediately visible on the OpenBus document that will need to be exposed. To see a list of these signals you'll need to use the **OpenBus Signal Manager**.

### Using the OpenBus Signal Manager

The **OpenBus Signal Manager** can be accessed from the **Tools** menu and it allows you to take finer control over which signals are to be exposed externally to the OpenBus document. A picture of this dialog is given in Figure 11.

The **Clocks** and **Resets** tabs will rarely need your attention as the default settings for these are usually adequate. The **Interrupts** tab will need your attention if you are planning on using any peripherals as interrupt sources. From this dialog you can allocate interrupts to the available interrupt channels on the main processor. In this design, interrupts won't be needed and so we can leave things in the default (unconnected) state.

The list of signals in the **External connection summary** can not be edited directly however this dialog serves as an excellent reference. All of the signals listed in this dialog will be exported to the parent schematic. The signals are grouped according to the component that controls them which makes it much easier to identify and locate the source of the different signals. For instance, when you link an OpenBus document to a parent schematic, it may not be immediately apparent where certain signals on the sheet symbol have come from. It is in this dialog box that you will find your answers.

| OpenBus Signal Manager                       |                            | ? 🛛       |

|----------------------------------------------|----------------------------|-----------|

| Clocks Resets Interrupts External connection | n summary                  |           |

| Name                                         | Port Name                  | Туре      |

|                                              |                            |           |

| 🛨 🍽 Video Capture Controller(VideoCapture)   |                            |           |

| 🖃 🍉 VGA 32-Bit TFT Controller(VideoDisplay)  |                            |           |

| ➡ TFT_CL[31]                                 | VideoDisplay_TFT_CL[31]    | Output    |

| TFT_DISP_ON                                  | VideoDisplay_TFT_DISP_ON   | Output    |

| TFT_M                                        | VideoDisplay_TFT_M         | Output    |

| TFT_POL                                      | VideoDisplay_TFT_POL       | Output    |

| TFT_STH                                      | VideoDisplay_TFT_STH       | Output    |

| TFT_STV                                      | VideoDisplay_TFT_STV       | Output    |

| TFT_RED[40]                                  | VideoDisplay_TFT_RED[40]   | Output    |

| TFT_GREEN[50]                                | VideoDisplay_TFT_GREEN[50] | Output    |

| TFT_BLUE[40]                                 | VideoDisplay_TFT_BLUE[40]  | Output    |

| ⊕-SRAM Controller(CaptureMem)                |                            |           |

| ⊕-SRAM Controller(DisplayMem)                |                            |           |

| ⊕-I2CM Controller(I2CM_W_1)                  |                            |           |

|                                              |                            |           |

|                                              |                            |           |

|                                              |                            |           |

|                                              |                            | ]         |

|                                              |                            | OK Cancel |

Figure 11. Using the OpenBus Signal Manager to identify the source of OpenBus signals.

### Creating a sheet symbol from the OpenBus Document

To link the OpenBus document to a parent schematic, you need to create a sheet symbol from the OpenBus document and place it on the parent schematic.

- 1. Open SpinningVideo\_FPGA.SchDoc

- 2. Select Design >> Create sheet symbol from sheet or HDL.

- 3. When the Choose Document to Place dialog box appears, select the SpinningVideo\_OB.OpenBus document and click OK.

- 4. A large sheet symbol will be attached to the cursor. Position it where you want to place it on the schematic page and click once to commit the placement.

| U_SpinningVideo_OB<br>SpinningVideo_OB.OpenBus |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                | WB_PRTIO_1_PAO[7.0]<br>VideoDisplay_TFT_CL[3.1]<br>VideoDisplay_TFT_DISP_ON<br>VideoDisplay_TFT_DISP_ON<br>VideoDisplay_TFT_POL<br>VideoDisplay_TFT_RD[4.0]<br>VideoDisplay_TFT_RED[4.0]<br>VideoDisplay_TFT_RED[4.0]<br>VideoDisplay_TFT_BLUE[4.0]<br>CaptureMem_SRAM_CE<br>CaptureMem_SRAM_CE<br>CaptureMem_SRAM_CE<br>CaptureMem_SRAM_OE<br>CaptureMem_SRAM_B3_E<br>CaptureMem_SRAM_B3_E<br>CaptureMem_SRAM_B1_E<br>CaptureMem_SRAM_B1_E<br>CaptureMem_SRAM_B1_E<br>CaptureMem_SRAM_B1_E<br>CaptureMem_SRAM_B1_E<br>CaptureMem_SRAM_0CE<br>DisplayMem_SRAM0_CE<br>DisplayMem_SRAM0_UB<br>DisplayMem_SRAM0_UB<br>DisplayMem_SRAM0_LB<br>DisplayMem_SRAM1_CE<br>DisplayMem_SRAM1_CE<br>DisplayMem_SRAM1_CE<br>DisplayMem_SRAM1_CE<br>DisplayMem_SRAM1_CE<br>DisplayMem_SRAM1_CE<br>DisplayMem_SRAM1_CE<br>DisplayMem_SRAM1_CE<br>DisplayMem_SRAM1_CE<br>DisplayMem_SRAM1_CE |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                | Display Mem_SRAM1_LB<br>I2CM_W_1_SDATAO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                | I2CM_W_1_SCLK_EN<br>I2CM_W_1_SDATA_EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                | I2CM_W_1_SCLKO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Figure 12. Creating a sheet symbol from an OpenBus document

The sheet entries on the newly placed sheet symbol have been loosely grouped with inputs on the left and outputs on the right. You must now go through a process of unraveling all of these sheet entries so that you can connect them to the port plugins on the NanoBoard more easily.

#### Wiring up the Top Level Schematic

To line the sheet entries up with the port plugins and to complete the top level schematic, you'll need to place a number of components. You'll find these libraries in the Libraries \FPGA folder of your Altium Designer installation.

- 1. From the FPGA NB2DSK01 Port-Plugin.IntLib:

- CLOCK\_BOARD

- LED

- NEXUS\_JTAG\_CONNECTOR

- SHARED\_MEM\_DAUGHTER

- SRAM\_DAUGHTER0

- SRAM\_DAUGHTER1

- TEST\_BUTTON

- TFT\_LCD

- 2. From the FPGA Peripheral Board 01 Port-Plugin.IntLib:

- VIDEO\_INPUT

- VIDEO\_INPUT\_CTRL

- 3. From the FPGA Generic.IntLib:

- INV

- IOBUF (x2)

- J4S\_4B

- NEXUS\_JTAG\_PORT

- 4. A completed version of the SpinningVideo\_FPGA.SchDoc schematic is given in Figure 13. Use this as a guide to position the port plugin components around the sheet symbol and then reorder the sheet entries so that they will line up nicely with them.

- 5. Once you have completed wiring up the schematic, select **Tools** » **Annotate Schematics Quietly...** to annotate the design by giving each component a unique designator.

- 6. Compile the design by selecting **Project** » **Compile FPGA Project SpinningVideo.PrjFpg**. Fix any compilation or wiring errors as necessary and save your work.

Figure 13. The Completed top-level schematicConstraining the Design

At this point we have completed the bulk of the FPGA design but there is one additional step that we need to go through before we can run it on the Desktop NanoBoard. Constraining an FPGA design is the process of defining the specific FPGA pins that you want each of the signals in your design to appear on. This is an important step as it will ensure that the FPGA design is able to interact with NanoBoard resources that have been hardwired to the FPGA daughter board.

When defining constraints, it is possible to hardcode them into the top-level schematic sheet but this is not advisable. The reason for this is because it binds the design to a specific device and limits your ability to retarget a different FPGA should the need arise. A much better approach is to store constraint information in a separate location to the schematic. Altium Designer implements this approach using a set of pre-built and user-definable constraint files which can be added to the FPGA project.

### Auto-configuring projects running on the Desktop NanoBoard

| Connected |                   | 1                        | *                    |

|-----------|-------------------|--------------------------|----------------------|

| TDI       |                   | Configure Fpga Project 🔸 | SpinningVideo.PrjFpg |

| Live      | NanoBoard-NB2-DSK | Instrument               | New FPGA Project     |

|           | Nanoboard-NB2-DSN | About                    |                      |

#### Figure 14. Creating a configuration automatically

In order to make the process of targeting your design to the Desktop NanoBoard, Altium Designer includes a handy autoconfiguration feature. By utilizing some smarts that have been built into the NanoBoard's firmware, Altium Designer is able to probe the Desktop NanoBoard and determine exactly what daughter and peripheral boards are connected. A set of predefined constraint files will then be loaded and grouped together into a configuration that targets your specific hardware setup.

| Constraint Filename         NB2DSK01_07_DB30_04           NB2DSK01_07_DB30_04_Mapping.Constraint         Image: Constraint           DB30.04.Constraint         Image: Constraint           NB2DSK01.07.Constraint         Image: Constraint           P801.04.Constraint         Image: Constraint           P801.05.Constraint         Image: Constraint           P802.05.Constraint         Image: Constraint           P803.05.Constraint         Image: Constraint | Constraint Files                       | Configurations      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------|

| DB30.04.Constraint         Image: Constraint           NB2DSK01.07.Constraint         Image: Constraint           PB01.04.Constraint         Image: Constraint           PB02.05.Constraint         Image: Constraint                                                                                                                                                                                                                                                    | Constraint Filename                    | NB2DSK01_07_DB30_04 |

| NB2DSK01.07.Constraint<br>PB01.04.Constraint<br>PB02.05.Constraint<br>C                                                                                                                                                                                                                                                                                                                                                                                                  | IB2DSK01_07_DB30_04_Mapping.Constraint | ✓                   |

| PB01.04.Constraint PB01.04.Constraint PB02.05.Constraint                                                                                                                                                                                                                                                                                                                                                                                                                 | DB30.04.Constraint                     | $\checkmark$        |

| PB02.05.Constraint                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IB2DSK01.07.Constraint                 | $\checkmark$        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2B01.04.Constraint                     | $\checkmark$        |

| PB03.05,Constraint                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2802.05.Constraint                     |                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 'B03.05.Constraint                     | $\checkmark$        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                        |                     |

Figure 15. Example of a configuration created from the Autoconfigure utility

To auto-configure your FPGA design to run on a Desktop NanoBoard:

- 1. Make sure your Desktop NanoBoard is connected to your PC and powered on.

- Select View » Devices View or click on the Devices View icon

in the toolbar.

- 3. In the **Devices View**, ensure that the **Live** checkbox is checked. You should see a picture of the Desktop NanoBoard in the upper region of the display.

- 4. Right-click the Desktop NanoBoard icon and select **Configure FPGA Project » SpinningVideo.PrjFpg**.

- Altium Designer will take just a few moments to probe the Desktop NanoBoard and create a new configuration. Click OK to accept the new configuration.

You may notice that a new **Settings** folder has been added to the project. In this folder you will find a **Constraint Files** folder with all of the newly added constraint files.

Several of the files will have a 'shortcut' Symbol. Altium Designer uses this notation to indicate files which are not stored in the main project folder. These particular files are all pre-defined

| Projects                               | <b>▼</b> × |

|----------------------------------------|------------|

| Workspace1.DsnWrk                      | orkspace   |

| SpinningVideo.PrjFpg                   | Project    |

| File View     Structure Editor         | ) 🚺        |

| 🗆 🔊 SpinningVideo.PrjFpg *             | B          |

| 🖃 🚞 Source Documents                   |            |

| 🖃 🖵 SpinningVideo_FPGA.SchDoc          | D I        |

| 🔙 SpinningVideo_OB.OpenBus *           |            |

| 🖃 🛄 Settings                           |            |

| 🖃 🛄 Constraint Files                   |            |

| 🎭 DB30.04.Constraint                   | B          |

| NB2DSK01.07.Constraint                 | <b>B</b>   |

| 🖏 PB01.04.Constraint                   | B          |

| Section 2015 PB02.05. Constraint       | B          |

| Section 2015 PB03.05. Constraint       | B          |

| NB2DSK01_07_DB30_04_Mapping.Constraint | E          |

Figure 16. Constraint files that have been added to the project by the autoconfigure utility.

constraint files that are shipped with Altium Designer. They are specific to the various peripheral and daughter boards that they represent and should NOT be edited as changes made to these files will affect all other projects that you build for the Desktop NanoBoard.

The constraint file that has been highlighted in Figure 16 was automatically created by the auto-configure process and is stored with the project. This file defines where the peripheral boards are located on the Desktop NanoBoard.

The auto-configuration process deals with the mapping of ports defined on the top-level FPGA schematic and their target FPGA pins. There are, however, additional constraints (such as the clock frequency) that are important for the design but which can not be handled automatically. In order to capture this information, it is best to create another constraint file that is reserved for this information and add it to the configuration.

To create a new constraint file and add it to the configuration:

- 1. Right-click the SpinningVideo.PrjFpg project in the Projects panel and select Add New to Project » Constraint File.

- 2. Select File » Save As ... to save the file. Give it a meaningful name such as MyConstraints.Constraint and click OK.

- 3. Right-click the SpinningVideo.PrjFpg project in the Projects panel and select Configuration Manager ... .

- 4. Locate MyConstraints.Constraint in the Constraint Files columns and check the box in the Configurations column to add it to the existing configuration.

- 5. Click OK to close the Configuration Manager and save your changes.

| Configuration Manager For SpinningVideo.PrjFpg               |                                                          |

|--------------------------------------------------------------|----------------------------------------------------------|

| Constraint Files                                             | Configurations                                           |

| Constraint Filename 🛆                                        | NB2DSK01_07_DB30_04                                      |

| DB30.04.Constraint                                           | ✓                                                        |

| NB2DSK01.07.Constraint                                       | $\checkmark$                                             |

| PB01.04.Constraint                                           | ✓                                                        |

| PB02.05.Constraint                                           | $\checkmark$                                             |

| PB03.05.Constraint                                           | $\checkmark$                                             |

| NB2DSK01_07_DB30_04_Mapping.Constraint                       | $\checkmark$                                             |

| MyConstraints.Constraint                                     | <u> </u>                                                 |

| Configurations Add Delete Rename Constraint Files Add Remove | e Force Columns Into View <u><u>D</u>K <u>C</u>ancel</u> |

Figure 17. Adding your own constraint file to the configuration

To add a clock constraint to the CLK\_BRD signal:

- 1. Open MyConstraints.Constraint.

- 2. Select Design » Add/Modify Constraint ... » Port ... .

- 3. In the Add/Modify Port Constraint dialog:

- Set the Target to CLK\_BRD

- Set the Constraint Kind to FPGA\_CLOCK\_FREQUENCY

- Set the Constraint Value to 50MHz.

- 4. Click OK to close the Add/Modify Port Constraint dialog.

5. Observe that a new constraint record has been added to MyConstraints.Constraint. Save your work.

**Record**=Constraint | **TargetKind**=Port | **TargetId**=CLK\_BRD | **FPGA\_CLOCK\_FREQUENCY**=50MHz

Figure 18. A clock frequency constraint

## **Building the FPGA design**

Once the FPGA design has been defined along with its constraints, you are now ready to build it. Building an FPGA design is the process of compiling and synthesizing your entire FPGA design into a configuration bit file that can be downloaded and run from the target FPGA device. Altium Designer standardizes the way you build an FPGA design so that it is vendor independent. You'll recall that a copy of the Vendor tools for the specific device you are targeting was listed in the "What you'll need" section of this tutorial. Altium Designer needs these vendor tools in order to place and route the design but the interaction with these back end tools will be largely transparent to the user.

To build an FPGA design:

- 1. Make sure your Desktop NanoBoard is connected to your PC and powered up.

- 2. Select View » Devices View or click on the Devices View icon 🎯 in the toolbar.

- 3. Ensure that the **Live** checkbox is checked. You should see a picture of the Desktop NanoBoard in the upper region of the display and an icon of the Spartan3 FPGA in the middle region.

- In the drop down list just below the Spartan3 icon, ensure that the SpinningVideo / NBD2DSK01\_07\_DB30\_04 project / configuration pair is selected.

- Locate the Compile, Synthesize, Build, Program FPGA buttons running left to right just below the Desktop NanoBoard icon. As this is the first time you have built your design, the colored indicators on each of the buttons will appear RED. Click once on the words Program FPGA to begin the build process.

- 6. As the build process progresses, the colored indicator from each stage will turn yellow while it is processing and then green when completed successfully. The process of building the design may take several minutes to complete. You can observe the progress of the build from the **Messages** and **Output** panels which can be accessed from the **System** panel tab in the lower right section of the Altium Designer workspace.

| S Altium Designer 6.8 (Beta Build 11226) - Wo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | kgroup [Workspace1.DsnWrk] - Devices - SpinningVideo.PrjFpg, Licensed to License Store - HQ |                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------|

| DXP Eile View Project Tools Hard Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Processors Window Help Devices.FpgaFlow 🔹 💿 🗸 🕐                                             |                 |

| 📘 🗋 🧀 💭 🗊 🌮 🎜 🛛 USB JTAG (0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | - 😰 III                                                                                     |                 |

| Projects 💌 🖉 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 📑 SpinningVideo_OB.OpenBus 🛛 🤡 Devices 🛛 📑 SpinningVideo_FPGA.SchDoc                        | »               |

| Workspace1.DsnWrk 🔹 Workspace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                             | *               |

| SpinningVideo.PrjFpg Project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Connected                                                                                   | ~               |

| File View     Structure Editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                             | TDO             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                 |

| SpinningVideo.PrjFpg *     Source Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Live NanoBoard-NB2-DSK1 V1.1.23                                                             |                 |

| E SpinningVideo_FPGA.SchDoc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                             |                 |