# マルチチャンネルデザインの 概念

#### 概要

Article AR0112 (v1.0) December 9, 2003 このアーティクルでは、DXPが装備しているマルチチャンネルの設計機能を紹介します。チャンネルごとに共通あるいは分配させるべきネットの取り扱い方や、PCBでの各チャンネルのクラスとルームについて解説します。

DXPでは、チャンネル内に他のチャンネルをネストして配置することができるマルチチャンネルデザインを装備しています。

デザインには同じ回路の繰り返しが含まれる場合が多くあります。例えば、ある基板では同一回路を32回も繰り返し使っていたり、あるいは8つの同一回路のサブチャンネルをそれぞれに持つ4バンクで構成している場合などがあります。従来の回路図入力ではこういった設計を、PCBレイアウトと関連付けるために"フラット階層"設計で対処せざるを得ず苦労してきました。回路図入力時の初期段階では、回路図のコピー・アンド・ペーストで比較的容易に作業できますが、回路図プロジェクトに一旦修正が発生すると、今まで作業した回路図の書き直しは困難でした。DXPはこういった繰り返しの多いプロジェクトに、一つのシートを参照できる効果的な真のマルチチャンネルデザインの機能を提供しています。ただ一枚の回路図を修正してプロジェクトを再コンパイルするだけで、全チャンネルに渡って必要な変更を反映させることができます。また DXP はマルチチャンネルだけでなく、回路図のネストもサポートしています。

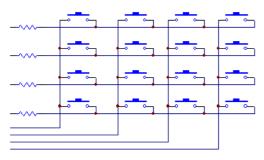

下図のような 16 個のキーパッドを持つ回路図を例に挙げて説明します。

このデザインは、DXPの回路図エディタでわずか数分で書き上げることができます。しかし、後に、キーパッドのシンボルやパラメータを修正する必要がある場合や、現状の 4x4 を 10X12 に拡張したい場合にはどうでしょう?

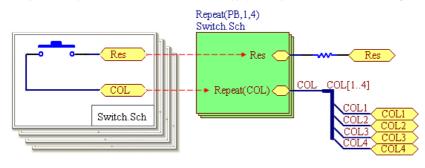

グループ編集ツールの助けを借りたとしても、この 修正はひどく退屈でエラーも生じやすい作業になり ます。そこで回路図の2枚のシートに2種のコンポーネント(抵抗とスイッチ)だけをそれぞれ配置し たと仮定してみます。上階層のシートシンボルに Repeatパラメータを記述してあれば、DXPのコンパイラは1枚のシートを参照し仮想の複製(チャンネル)を指定した個数分だけ作成します。まず抵抗を配置した回路図でスイッチを4個並べるためにスイッチを配置したシートを4回リピートし1行に相

当する部分を作成します。更にトップ階層で抵抗1個とスイッチ4個並んだこの回路図を4回リピートして回路全体を形成させます。以上の操作でマルチチャンネルが複数のチャンネル内に収められ、それに応じた接続のマトリクスが確立されています。

#### マルチチャンネルデザインの概念

このマルチチャンネルの機能により設計者の作業が容易になり、上の例ではスイッチや抵抗に対しての変更を何度も行う必要は無く、一回の修正で行うことができるようになります。また、スイッチ配列のマトリックスを拡張したい場合は、シートシンボル内の Repeat 記述を単に修正するだけの作業で行えるようになります。

マルチチャンネルデザインを素早く作成するには、DXPでのプロジェクト内での接続方法に慣れている必要があります。

### マルチチャンネル接続

他のマルチシートデザインの場合と違いマルチチャンネルデザインでは Net Identifier scope の設定を Hierarchical (sheet symbol <-> port)にしておく必要があります。Project Options ダイアログでこの設定を Automatic にしておくのが最良ですが、繰り返されるシートに信号を伝達させる唯一の方法は、親シートのシートエントリーに対応した子シートのポートへの接続であると理解してください。この制限はシートエントリーがポートやネットラベルと異なり、Repeat 記述で作成される繰り返されたチャンネルを扱うように作られているからです。

マルチチャンネル設計で利用できるシート間の接続には、全てのチャンネルに共通したネットと各々に固有なネットの2種類があります。これらのタイプを上記のキーパッドの例で説明すると、各スイッチには抵抗に直接接続させるピンがありました。これは各チャンネルの同じノードが親シートの1つのノードに対し互いに結ばれる共通のネットで下図のように接続されています。

この方法は DXP のマルチチャンネルデザインで一番簡単なネット接続の方法で、シートエントリーとチャンネルデザイン内の一致するポートが接続されます。

スイッチのもう片側は縦方向のスイッチ同士を結んでいます。重複したチャンネルから接続情報の伝達のために、Repeat 記述がシートエントリーに必要となり

この図は、2種類の接続タイプを表しています。

2つのシートエントリーに違いがあることに注意して下さい。シートエントリーRes は、同じ名前のポート同士をそれぞれ接続します。シートエントリーCOLにはポート名に Repeat コマンドが付加されています。これはネットラベルが付けられたワイヤーやバスに対し、コピーされた 4 枚のシートから 4 本のネットが引き出されていることを意味しています。このポイントから必要なノードを分離して接続したり、さらにポートを通って別の階層へ接続することができます。

一旦 DXP の接続構造 に従ったマルチチャン ネルプロジェクトを作 成すれば、各チャンネ ルのコンポーネント名 称の割り当て方が理解 できるでしょう。

ます。

### チャンネルの指定

チャンネルとは仮想的なシートであり DXP のシンクロナイザーは各チャンネルに他と区別したルームを割り当てます。しかしその前にコンパイラで、全チャンネル内の全コンポーネントに対して固有な名称を割り付けておくことが必要です。ネスト化したチャンネルを使用している場合には、これらの名称は、Project Options ダイアログの Multi-Channel タブ(コンポーネントやルームの番号をどのように設定するかの図)で設定した内容に従って割り当てられます。

基本的には2種類の設定方法があります。1つ目はルームとコンポーネントの名称をフラットまたは階層的に割り当てるかです(もしデザインにネストしたチャンネルが含まれる場合、この方法が重要になります)。2つ目はインデックスに数字またはアルファベットのサフィックスを付加するかです(両方を考慮するオプション設定もありますが、もう一度、ネストしたチャンネルの名称が明確になるだけです)。

コンポーネントデシグネータに指定するフォーマットには、特定のチャンネルとルーム名を含んでいますが、必ず必要というわけではありません。通常のデシグネータフォーマットでは、コンポーネントとチャンネルの両方のプリフィックスとサフィックスが含まれます。7つの予約されたキーワードのうちの2つ(\$Componentと\$RoomName)は、これらを自動で行います。

\$Component は、\$ComponentPrefix \$ComponentIndex の組み合わせになっています。例えばコンポーネントパート U3A は、プリフィックス(U)とインデックス(3A)から成り立っています。同様に \$RoomName は、チャンネルプリフィックスとサフィックスの組み合わせですが、その正式な形は選択したスタイルを指定したデザインおよびルームにより変化します。もしデザインがネスト化したチャンネルを含まないのであれば、階層的部分のスタイルは無関係に、数字またはアルファベットの部分のみ\$RoomName で示されたチャンネル表記に変化します。しかしデザインにネスト化したチャンネルがあり、スタイルを指定する階層構造のルームを使用している場合は、\$RoomName を

**\$ChannelPrefix・\$ChannelAlpha・\$ChannelIndex** に置き換えることはできません。これは、**Repeat** 記述で使用したチャンネル名から、マルチレベルプリフィックスを構築する為です。

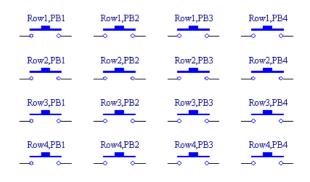

例えば先に解説したキーボードのプロジェク

トで説明すると、Room Naming Style を Numeric Name Path に設定した場合、

\$RoomName の記述は Level Separator と

Designator Format がコンマで区切られ、デザインをコンパイルした後の 16 個のボタンは図のように記述されます。

Alpha Name Path を選択した場合、デシグネータは、RowA,PBA や RowA,PBB などになります。 Mixed Name Path を選択していた場合なら、RowA,PB1 や RowA,PB2 などとなります。しかし、もしフラット構成を選択してい

た場合には、Row チャンネルは参照されずデシグネータが PB1 から始まり PB16 で終わるか、PBA から始まり PBP で終了するような名称が割り当てられます(数字またはアルファベットのサフィックス)。もちろんそれは、Designator Format フィールドで指定したコンポーネント自体への参照を除外するための機能ではなく、各チャンネルにコンポーネントが含まれる場合にのみ実行されます。

#### マルチチャンネルデザインの概念

これらは物理的よりむしろ論理的にデジグネータを表示するためのオプションなので、余りに字数が多くなりすぎて PCB に適合しなくなることを憂慮する必要は無く、デシグネータに希望する情報が含まれていることを確認してください。

## PCB 設計者の為のルーム

マルチチャンネルデザインは、回路設計者だけでなく誰でも役立ちます。PCB 設計者の利点は、ボード外形の近くに自動で置かれたそれぞれのルーム内へチャンネルのコンポーネントを展開することです。ルームに基づいた部品配置のツールは、マルチチャンネルデザインでのレイアウト作業において強力な手助けとなるでしょう。

DXP の Situs オートルーターは、ルーム内に含まれた全ての接続を配線できるルームの設定機能を備えています。逆に、Unrouting ツールはルームオプションを備えています。各チャンネルに対応するコンポーネントは、同じ Channel Offset の値が割り当てられており、セレクトまたは編集する際には一括して実行することが可能です。

さらに特徴的な機能として、あるルームから他のルームへとフォーマットをコピーすることができることです。この機能を使えば1つのルームに行った変更を即座に別のルームへ反映させることができます。コピー元とコピー先のルームが同じチャンネルクラス(同じシートから複製されたことを意味します)にある場合、更新は一度に全ての同一クラスメンバー全体に反映できます。フォーマットをコピーする内容は、ルームのサイズや形状の変更・フットプリントの配置や配線まで制限を設定することができます。更に、このようなルームに存在する配線をどれくらい遠くに移動させるかを制御することもできます。

マルチチャンネルデザインを最大限に活用できるように、ボード設計者の為に PCB エディタに多くの ツールが追加されました。一例をあげるなら、ボードの反対側にルームごとオブジェクトを移動した い場合は、 Design » Rooms のサブメニューMove コマンドで移動中に L キーを押すと、配置と配線を 含むルーム全体が層を変えて移動したことが確認できるでしょう。

マルチチャンネルデザインの根本的に有利な点、それが回路設計者だけでなくボード設計者の省力化にも寄与できる点です。もう同じ作業を32回も繰り返して行う必要はありません。

マルチチャンネルデザインの利点についての詳しい実例は、Altium\Examples\Reference Designs\Peak Detector フォルダの PCB プロジェクトを参照して下さい。

### 更新履歴

| Date       | Version No. | Revision            |

|------------|-------------|---------------------|

| 9-Dec-2003 | 1.0         | New product release |

Software, documentation and related materials:

Copyright © 2003 Altium Limited.

All rights reserved. Unauthorized duplication, in whole or part, of this document by any means, mechanical or electronic, including translation into another language, except for brief excerpts in published reviews, is prohibited without the express written permission of Altium Limited. Unauthorized duplication of this work may also be prohibited by local statute. Violators may be subject to both criminal and civil penalties, including fines and/or imprisonment. Altium, DXP, Design Explorer, nVisage, Nexar, Protel, P-CAD, Tasking, CAMtastic, Situs and Topological Autorouting and their respective logos are trademarks or registered trademarks of Altium Limited. All other registered or unregistered trademarks referenced herein are the property of their respective owners and no trademark rights to the same are claimed.